Inter-integrated Circuits also referred as I2C protocol is a serial, multi-master, half-duplex protocol used for communication between integrated circuits. I2C is a two-wire master-slave protocol in which slave can become a master if needed. Serial Data (SDA) and Serial Clock (SCL) are the wire of the I2C protocol.

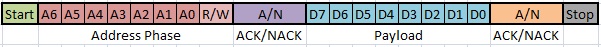

Below is the frame format for the 7 bit identifier I2C protocol,

Start Condition:

SDA goes from high to low when the SCL is high marks the start condition. SDA should not make a transition when SCL is high during the other phases of the I2C protocol.

Address Phase:

A slave in I2C protocol is identified by a 7 or a 10 bit identifier. This identifier along with the read/write bit forms the address phase of the I2C protocol. SDA line cannot make a transition from high to low or low to high when the SCL is high in the address phase. Data transition can only happen when the SCL is low. Read(1)/Write(0) bit is the bit that follows the slave identifier in the address phase.

ACK/NACK:

At the 9th clock pulse i.e. immediately after the address phase, if the SDA goes low, it is marked as an ACK in I2C protocol. An ACK from a slave means that the address sent out by the master during the address phase matches with the address of one of the slaves connected to the I2C bus.

If the SDA remains high at the 9th clock pulse, it represents a NACK i.e. the address sent out by the master does not match to the addresses of any of the slaves connected on the I2C bus.

Slave sends an ACK/NACK after the data phase to specify if the data was received successfully or not.Data Phase:

This is a data segment in I2C in bytes. Slave has to send an ACK/NACK for every byte received. Master can continue sending data if required without invoking the STOP condition.

Stop Condition:

SDA goes from low to high when SCL is high marks the stop condition. SDA should make a transition when SCL is high only during the START or STOP conditions.

After the STOP condition if the SDA and SCL both remain high means that the bus is free and can be used by other bus master.